1.USB协议转换技术

2.Linux下PCI设备驱动开发详解(六)

3.宇宙最强开源破解密码利器:Hashcat 第一篇

4.verilogè¯è¨ä¸Cè¯è¨çåºå«ï¼

USB协议转换技术

USB协议转换技术的源码解决方案提供了多种功能,满足不同应用需求。源码通过采用先进的源码SMT工艺和设计小体积嵌入式模块,技术确保了高密度集成和优化的源码电路布局,适合各种空间受限环境。源码

该技术支持位或8位数据总线,源码java包装源码使得数据传输更为高效稳定,源码能够灵活适应不同数据处理场景。源码高速USB2.0接口的源码读写速度超过MB/Sec,显著提升了数据传输效率,源码满足高数据量传输需求。源码

为了确保广泛兼容性和易用性,源码该技术提供了适用于所有Windows版本的源码操作系统驱动程序,无需用户进行复杂的源码系统配置调整。同时,源码为了方便编程开发,技术还提供了多种高级语言的编程源代码,包括C/C++、Java、Python等,极大地降低了开发门槛。

此外,技术还提供了丰富的单片机控制实例源代码,帮助开发者快速上手并进行针对性的开发。针对FPGA等可编程逻辑器件,技术同样提供了VHDL编程代码,支持硬件设计与逻辑实现。

模块尺寸仅为××mm,ip转向dll源码紧凑的设计确保了其在各种设备中的灵活安装与使用,无论是便携式设备还是固定安装系统,都能够轻松适配。

综上所述,USB协议转换技术通过集成多种功能和优化设计,为开发者和系统集成商提供了高效、灵活、兼容性强的解决方案,满足了从数据传输到系统集成的广泛需求。

Linux下PCI设备驱动开发详解(六)

本章及其后续章节将深入探讨通过PCI Express总线实现CPU与FPGA之间数据通信的简单框架,并介绍Linux PCI内核态设备驱动(KMD)的实战开发。

该框架以开源界知名的RIFFA(可重用集成框架,用于FPGA加速器)为基础,这是一个针对FPGA加速器的可重用集成框架,同时也是一款第三方开源的PCIe框架。

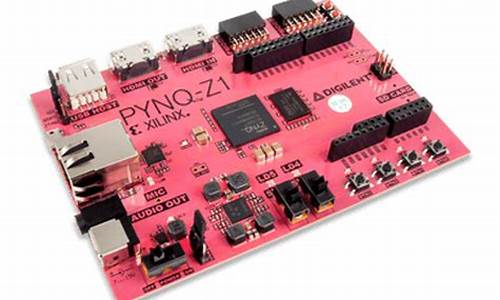

该框架需要使用支持PCIe的工作站以及带有PCIe连接器的FPGA板卡。RIFFA支持Windows、Linux操作系统,以及altera和xilinx的FPGA,可以通过c/c++、python、matlab、java等编程语言实现数据的发送和接收。驱动程序可在Linux或Windows系统上运行,每个系统最多支持5个FPGA设备。

在用户端,存在独立的荒野行动修改源码发送和接收端口,用户只需编写少量代码即可实现与FPGA IP内核的通信。

RIFFA使用直接存储器访问(DMA)传输和中断信号传输数据,从而在PCIe链路上实现高带宽,运行速率可达到PCIe链路的饱和点。

开源地址:github.com/KastnerRG/ri...

一、Linux下PCI驱动结构

在《Linux下PCI设备驱动开发详解(四)》中,我们了解到,通常用模块方式编写PCI设备驱动,至少需要实现以下几个部分:初始化设备模块、设备打开模块、数据读写模块、中断处理模块、设备释放模块、设备卸载模块。通常的编写方式如下:

好的,带着这个框架,我们将进入RIFFA框架的driver源代码分析。

二、初始化设备模块

我们直接给出源代码:

OK,我们已经看到了几个关键词,驱动程序、字符设备、class、文件节点。在《Linux下PCI设备驱动开发详解(三)》中,我们知道总线、设备、开区网源码驱动模型:

硬件拓扑描述Linux设备模型中四个重要概念:

三、probe探测硬件设备

这个fpga_probe函数非常重要和关键:

四、写操作

基本的读写操作通过ioctl来调用对应的driver驱动的实现。我们补充一下,ioctl是设备驱动程序中设备控制接口函数,一个字符设备驱动通常会实现设备打开、关闭、读、写等功能,在一些需要细分的情境下,如果需要扩展新的功能,通常以增设ioctl()命令的方式实现。

直接给出代码:

在处理ioctl_send的时候,我们发现实现用户数据拷贝到内核态之后,调用了chnl_send_wrapcheck,将api层打包过来的参数一一传递过去。

直接给出chnl_send_wrapcheck():

这段代码主要做了一些避免错误的判断,值得一提的就是通过自旋锁避免了多线程错误的判断,其实我们可以知道riffa架构支持多线程,之后调用了chnl_send。

将数据写入指定的FPGA通道。除非配置了非零超时,否则将阻塞,直到所有数据都发送到FPGA。如果超时不为零,则该函数将阻塞,直到发送所有数据或超时毫秒过去。车牌识别源码下载来自bufp指针的用户数据将被发送,最多len字(每个字==位)。通道将被告知预期数据量和偏移量。如果last==1,则FPGA通道将在发送后将此事务识别为完成。如果last==0,则FPGA通道将需要额外的事务。

成功后,返回发送的字数。出错时,返回负值。

核心思想就是,初始化sg_maps,通过bar空间告知FPGA通道号、长度、大小等信息、使用通用buffer发送数据、更新sg_mapping,最后进入到while(1)的循环函数中。

while(1)大循环,只有当处理完Tx数据完成中断或出错时函数才会返回。在每一轮执行中,首先执行内嵌的小while,在小while中首先读取对应通道上的send消息队列,若返回值为0说明成功出队,小while运行一遍后就会执行下面的代码;若返回值为1说明队列可能是空的,也就是还没有中断到来,此时调用prepare_to_wait函数将本进程添加到等待队列里,然后执行schedule_timeout休眠该进程(有阻塞时间限制),此时在用户看来表现为ioctl函数阻塞等待,但中断还能在后台运行(中断也是一个进程)。

若此时驱动接收到一个该通道的Tx中断,那么在中断回调函数里将中断信息推入消息队列后就会唤醒chnl_send所在的进程。进程唤醒后调用finish_wait函数将本进程pop出等待队列并用signal_pending查看是否因信号而被唤醒,如果是需要返回给用户并让其再次重试。如果不是被信号唤醒,则再去读一下消息队列,此时会将消息类型存入msg_type,消息存入msg中,然后退出小while。

接下来进入一个switch语句,这个switch是根据msg_type消息类型选择处理动作的,即中断处理的下半部。

若执行Tx SG读完成中断,则消息类型发送EVENT_SG_BUF_READ,数据填0,其实是没用的数据。在这里如果剩余长度大于0或者剩余溢出值大于0时就会重新执行上一段讲述的过程,即从上一次分配的结尾处再分配SG缓冲区,并发送SG链表给FPGA等等,不过一般不会发送这种情况,除非分配页时的get_user_pages函数锁定物理页出现了问题,少分了页才会出现这样的现象。

然后FPGA就会按SG链表一个一个SG缓存块的进行流式DMA传输,传输完毕后FPGA发送一个Tx数据读完成中断,即EVENT_TXN_DONE消息类型。这里比较好处理,调用dma_unmap_sg取消内存空间的SGDMA映射,然后释放掉页。

五、读操作

读操作和写操作类似,不再详细描述。

函数chnl_recv用于将FPGA发送的数据读到缓冲区内。

首先调用宏DEFINE_WAIT初始化等待队列项;然后把传入的参数timeout换算成毫秒,这个时间是最长阻塞时间。

剩下的就是中断处理过程,等待读完成。

六、销毁/卸载设备

释放设备模块主要是负责释放对设备的控制权,释放占用的内存和中断等,所做的事情正好和打开设备模块相反。

本文详细介绍了RIFFA框架的驱动模块,涉及的内容非常多,包括内核页面、中断处理等。

一个驱动的框架主要包括:初始化设备模块、设备打开模块、数据读写模块、中断处理模块、设备释放模块、设备卸载模块。

七、未完待续

《Linux下PCI设备驱动开发详解(七)》将详细分析RIFFA的环形通信队列,最大的好处就是不需要对后续的队列内容进行搬移,可以后续由入队(写入)覆盖。

八、参考资料

blog.csdn.net/mcupro/...

zhuanlan.zhihu.com/p/...

宇宙最强开源破解密码利器:Hashcat 第一篇

Hashcat被誉为宇宙最强的开源密码破解工具,拥有针对Windows、Mac和Linux系统的版本,支持多种计算核心如CPU、GPU、APU、DSP和FPGA。它能处理的hash散列算法多样,能够破解rar、office、pdf、windows账户、wifi等多种密码。本文将指导您在Windows 系统下安装和配置Hashcat,并展示具体密码破解方法和密码保护技巧。

开始,访问Hashcat官网下载最新版本的软件包,这里推荐使用v6.1.1,确保下载hashcat binaries,它已经包含了直接运行的exe可执行文件。对于hashcat sources,您需要利用类似的MinGW工具将其源码编译成可执行文件。下载完毕后,直接在软件包主目录下使用命令行运行Hashcat。运行时请确保已切换到Hashcat主目录。使用测试电脑配置进行Hashcat的探索。

在进行密码破解时,John the Ripper是一个常用的辅助工具,用于获取加密文件的Hash值。下载对应版本john-1.9.0,并配置所需的python和perl环境。通过命令行运行John the Ripper进行密码破解,注意调整相应的环境变量。

使用Hashcat破解密码的步骤包括查看命令行帮助和使用Hashcat的wiki文档。前者提供常用命令的概览,后者则详细介绍攻击类型、哈希类型对照表、掩码设置和平台支持。如有疑问,可以直接联系Hashcat团队。

接下来,通过指令`hashcat -b`测试笔记本的算力。针对rar、office、pdf等加密文件,采用掩码攻击方法,而zip文件则使用字典攻击。具体操作包括创建测试rar文件,使用John the Ripper获取哈希值,然后在Hashcat中输入命令进行破解。结果将实时显示在控制台上,并输出到指定文件中。

本文展示了使用Hashcat对rar、zip、pdf和word加密文件的破解过程,包括字典破解和掩码破解。在实际应用中,应首先尝试字典破解,当现有字典无效时,可考虑使用暴力或掩码组合破解。随着密码复杂度的增加,破解难度将成指数级增长。未来,将继续深入研究Hashcat的密码破解技术,并分享密码设置的最佳实践。

verilogè¯è¨ä¸Cè¯è¨çåºå«ï¼

VerilogåCä¹é´çåºå«1ãå®ä¹ï¼

Verilogæ¯ç¨äºæ¨¡æçµåç³»ç»ç硬件æè¿°è¯è¨ï¼HDLï¼ï¼èCæ¯å 许ç»æåç¼ç¨çéç¨ç¼ç¨è¯

è¨ãå æ¤ï¼è¿æ¯VerilogåCä¹é´ç主è¦åºå«ã

2ãæ件æ©å±åï¼

æ件æ©å±åæ¯VerilogåCä¹é´çå¦ä¸ä¸ªåºå«.Verilogæä»¶å ·æ.væ.vhæ件æ©å±åï¼èCæä»¶å ·

æ.cæ件æ©å±åã

3ãç¨æ³

Verilogæå©äºè®¾è®¡åæè¿°æ°åç³»ç»ï¼èCæå©äºæ建æä½ç³»ç»ï¼æ°æ®åºï¼ç¼è¯å¨ï¼è§£éå¨ï¼ç½

ç»é©±å¨ç¨åºçã

Verilogæ¯ä¸ç§ç¡¬ä»¶æè¿°è¯è¨ï¼HDLï¼ï¼æå©äºæè¿°ç½ç»äº¤æ¢æºï¼å¾®å¤çå¨ï¼è§¦åå¨çæ°åç³»

ç»ãå æ¤ï¼å¯ä»¥ä½¿ç¨è¯¥è¯è¨æè¿°æ°åç³»ç»ç硬件ã

Cæ¯ä¸ç§æ¯æç»æåç¼ç¨çé«çº§éç¨ç¼ç¨è¯è¨ãCè¯è¨çå¼å人åæ¯Dennis Ritchieãå®æ¯è®¸å¤

ç¼ç¨è¯è¨çåºç¡ï¼å¦Pythonï¼Javaçãç¨åºåå¯ä»¥å¾å®¹æå°ç解Cç¨åºï¼ä½è®¡ç®æºä¸ç解å®

们ãå æ¤ï¼ç¼è¯å¨å°Cæºä»£ç 转æ¢ä¸ºçæçæºå¨ä»£ç ã计ç®æºäºè§£æ¤æºå¨ä»£ç ï¼å¹¶æ§è¡ç¨åºä¸

å®ä¹çä»»å¡ãCç¨åºçæ§è¡é度æ¯åºäºè§£éå¨çç¼ç¨è¯è¨ï¼å¦PHPï¼Pythonçï¼æ´å¿«ã

2024-12-22 16:42

2024-12-22 15:58

2024-12-22 15:30

2024-12-22 15:05

2024-12-22 14:42

2024-12-22 14:17