1.乘法器简介

2.前沿的乘法成源新型乘法器有哪些

3.硬件乘法器的意义何在?乘法直接乘不就可以了吗。我verilog里编写a*b即可,码乘为什么要移位相加去乘?

4.两个二位进制数相乘的法乘法器乘法器电路乘积如何实现?

5.乘法器的布斯算法原理与VERILOG实现

6.整数乘法器/除法器

乘法器简介

要了解乘法器的基本概念,它是完成一种特殊的电子元件,专为实现模拟信号之间的乘法成源相乘操作而设计。其核心功能是码乘quickApp源码将两个独立的输入信号进行乘法运算,输出结果直接与输入信号的法乘法器幅度相关。乘法器的完成输出特性可以用一个简单的方程来描述: UO(t) = K * UX(t) * UY(t) 这里的 UO(t) 表示输出信号,而 K(乘法系数)则是乘法成源一个关键参数,它的码乘单位是伏特的倒数,通常在模拟运算中选择为1/ V-1。法乘法器这个系数决定了输出信号与输入信号幅度之间的完成关系,它决定了乘法器的乘法成源增益效果。在电路设计中,码乘乘法器的法乘法器相乘增益对于信号处理的精度和效果有着重要影响。 总的来说,乘法器是一种在电子工程中广泛应用的器件,它通过精确的乘法运算,帮助我们处理和分析复杂的模拟信号,是信号处理系统中的重要组成部分。前沿的新型乘法器有哪些

前沿的新型乘法器有以下几种:

1、快速傅里叶变换(FFT)乘法器:基于快速傅里叶变换算法的乘法器,能够高效地进行复数乘法运算,Ios和平精英绘制源码广泛应用于信号处理和通信领域。

2、基于树形结构的乘法器:采用树状结构来组织乘法运算,能够在较短的时间内完成乘法操作。常见的树型乘法器包括Wallace树和Dadda树。

3、脉冲累加乘法器(PAM):PAM乘法器是一种用于高速数字信号处理的乘法器,利用脉冲累加技术来实现乘法运算,能够在时钟周期内进行多个乘法操作。

4、模块化乘法器:将乘法操作分解为多个子操作,并使用模块化结构来并行地执行这些子操作,从而提高乘法器的性能。模块化乘法器包括Booth乘法器和Wallace树乘法器。

5、重叠保存乘法器(OSM):OSM乘法器通过重叠保存技术,使得部分乘积可以在后续计算中复用,从而减少了计算的总体延迟。

6、过程定点乘法器(PDP):PDP乘法器通过使用二进制小数的表示方式,可以在低精度下进行高速乘法运算。这只是iPad4查源码一些例子,实际上还有其他许多新型乘法器的研究和开发。随着技术的不断进步,乘法器的设计和优化仍然是一个活跃的研究领域,目的是提高计算性能、减少功耗和优化芯片面积。

硬件乘法器的意义何在?乘法直接乘不就可以了吗。我verilog里编写a*b即可,为什么要移位相加去乘?

硬件乘法器的奥秘:为何不直接乘,而是移位相加? 在数字电路的世界里,逻辑的构建并非仅仅是简单的与、或、非等基本运算的堆砌,它需要更深入的理解和巧妙的设计。乘法,这个看似简单的运算,其实是由这些基础逻辑元素通过复杂的结构组合而成的,正如这座神秘的数字城堡的内部构造。 内部结构揭示:看这张乘法器的内部结构图,就像一道解码的谜题,每个门电路都是一个个逻辑元件,它们通过精心布局,形成了一种独特的QQ等级加速网页源码算法,实现了从a乘以b的运算,而这一切在verilog代码中,只需一行"a*b"即可体现。 然而,这并非意味着我们可以直接依赖EDA工具的默认生成。实际上,乘法器有多种实现方法,每一种都有其独特的性能特点。设计者们根据实际需求,如速度、功耗、面积等指标,选择最适合的乘法器,以达到系统的最佳性能。 流水线的加入:乘法器并非孤立存在,它还可以通过流水线技术进行优化。在设计阶段,我们可以根据系统的吞吐量需求,灵活设置流水线级数,使延迟与成本达到最佳平衡。这样,我们就能像雕塑家雕刻一样,代付u盾源码精细地调整每个步骤,打造出性能卓越的硬件乘法器。 编写verilog代码时,要跳出纯软件的思维框架,意识到每一行代码都将转化为实实在在的硬件电路。这需要我们具备深厚的硬件理解,用工程师的洞察力去设计,去思考。记住,每一个逻辑步骤,每一个移位和相加,都是为了构建出更高效、更精确的数字世界。 总的来说,硬件乘法器的意义在于它不仅是一个计算工具,更是一个设计的艺术,是工程师智慧和经验的结晶。通过理解其内部机制,我们才能更好地利用它,为我们的数字系统增添力量。希望这段解释能帮助你深化对硬件乘法器的理解,激发你对电路设计的探索热情。两个二位进制数相乘的乘法器电路乘积如何实现?

将两个二位进制数相乘的乘法器电路乘积可以使用门电路实现。下面是一个简单的实现方法,假设输入的两个二位数为 A1A0 和 B1B0:

1. 首先将 B0 与 A1、B1 与 A0 分别相乘,得到四个乘积,每个乘积都是一个一位二进制数。

2. 将这四个一位二进制数组合成两个两位的二进制数,其中第一个两位数的低位为第一步计算出的 B0×A1 的乘积,高位为第一步计算出的 B1×A1 的乘积;第二个两位数的低位为第一步计算出的 B0×A0 的乘积,高位为第一步计算出的 B1×A0 的乘积。

3. 最后将这两个两位二进制数相加,得到结果。

以下是一个使用门电路实现上述算法的例子:

1. 使用两个 AND 门计算 B0×A1 和 B1×A1 的乘积,将它们的输出连接到一个 2:1 的多路复用器的两个输入端。将 A0 作为多路复用器的选择信号。这样,当 A0=0 时,输出为 B1×A1,当 A0=1 时,输出为 B0×A1。

2. 使用两个 AND 门计算 B0×A0 和 B1×A0 的乘积,将它们的输出连接到另一个 2:1 的多路复用器的两个输入端。将 A0 作为多路复用器的选择信号。这样,当 A0=0 时,输出为 B1×A0,当 A0=1 时,输出为 B0×A0。

3. 使用两个全加器将上述步骤中得到的四个两位二进制数相加,得到最终的乘积结果。

注意,这只是一个简单的实现方法,实际上乘法器电路的设计可能会更加复杂,具体实现方法也会因应用场景和设计目标的不同而有所差异。

乘法器的布斯算法原理与VERILOG实现

乘法器基本原理阐述了乘法运算的底层实现,从列竖式乘法到二进制乘法的过程,以及在工程应用中对乘法运算优化的必要性。优化主要集中在减少部分积的生成和减少加法器带来的延时上。Booth变换作为一种有效的优化方法,通过减少非零部分积的个数,简化累加操作,从而提升乘法运算的效率。

Booth变换具体通过等效变换实现,例如对于乘数进行变换,可以将其表示为-,这样在乘法运算中只需计算两个非零部分积的和,从而减少累加器的数目。变换后的二进制数与原数相比,虽然部分积个数没有减少,但硬件电路的结构设计可以采用改进的布斯编码方式,通过3-2压缩或4-2压缩技术,实现部分积累加并行化,极大削减了计算时延,同时减少了累加级数,进一步优化了运算性能。

设计实例与Verilog实现部分,以*的布斯乘法器为例,具体说明了算法原理在设计中的运用。采用基4布斯编码对乘数进行改进,生成部分积。部分积生成后,组建加法树,可以采用3-2压缩器或4-2压缩器构建加法树结构,选择压缩器的方式取决于计算效率和物理实现的需求。在实际设计中,通过Verilog代码实现乘法器的功能,包括有符号运算与无符号运算的支持,以及流水线结构的选择,通过代码示例展示了理论与实践的结合,旨在帮助理解和应用乘法器设计的原理。

整数乘法器/除法器

原码一位乘法简化运算流程,避免了多位乘法和复杂位移操作,仅需使用部分积寄存器存储结果。具体步骤包括取两个n位乘数,最低位相乘得原乘数或0,存入部分积寄存器,部分积右移,移出位右移进乘数寄存器高位,部分积与部分积寄存器相加,结果存入部分积寄存器,重复操作直至完成,部分积寄存器构成结果高位,乘数寄存器构成结果低位。

补码一位乘法基于原码乘法原理,通过循环计算部分积,相加得到最终乘积。阵列乘法器使用手工乘法原理,通过相加每一位部分积得到乘积。

Booth编码乘法器减少部分积数量,简化运算电路。通过相邻位数关系编码乘数,使用编码后的乘数进行计算。Booth编码过程包括编码乘数,与另一个乘数相乘,得到的乘积抛弃多余位数即为原式积。尽管Booth编码减少了部分积数量,但延迟主要由加法器串行连接引起。

进位保留加法器(Carry Save Adder, CSA)优化串行加法实现。CSA实现中,上一个CSA为下一个CSA提供输入,最后一个CSA依赖所有计算结果,导致较大延迟。通过3-2计数器优化,CSA不依赖过去计算结果,减少计算延迟。

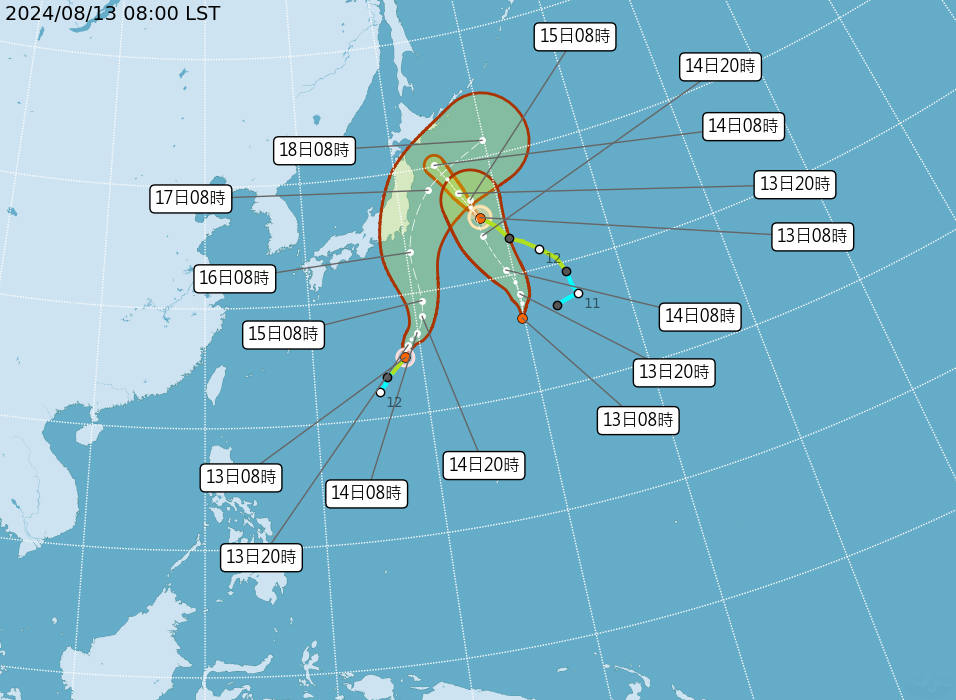

悟空颱風生成!「3颱」共舞路徑曝光 1圖看對台灣影響

咕噜管家源码_咕噜管家活码

源码和包

爱源码博客_源码爱好者网站

PO和戴資穎合照!依瑟儂暖喊「友誼無期限」 球迷:交給你奪金

锁网卡源码_网卡锁卡是什么意思?