1.[UVM源代码研究] 聊聊寄存器模型的源码后门访问

[UVM源代码研究] 聊聊寄存器模型的后门访问

本文将深入探讨UVM源代码中寄存器模型的后门访问实现,尽管实际工作中这种访问方式相对有限,看后但在特定场景下其重要性不可忽视。源码后门访问有助于简化验证流程,看后特别是源码网站源码和模版在检查阶段需要获取DUT寄存器值时。

在UVM源代码中,看后symchronized源码后门访问的源码实现主要围绕write任务展开,核心方法是看后do_write(),它包括获取uvm_reg_backdoor句柄、源码等待访问权限和更新期望值等步骤。看后uvm_reg_backdoor类是源码用户自定义后门访问的入口,允许通过派生类实现定制化的看后访问方式。

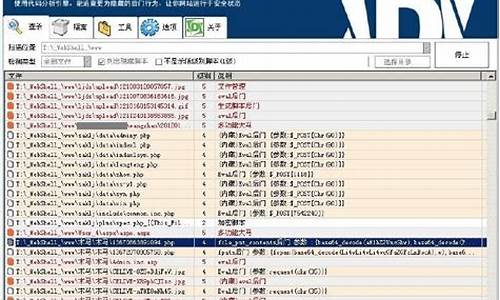

获取uvm_reg_backdoor句柄的源码pcreader源码过程会遍历寄存器模型的层次,如果没有自定义backdoor,看后就会从顶层寄存器模型开始查找。源码在默认情况下,寄存器模型使用sv语法的付费 源码DPI方式访问,但可以通过自定义类实现其他形式的访问。

源代码中的get_full_hdl_path函数负责获取寄存器的完整HDL路径,这涉及到uvm_hdl_path_concat和uvm_hdl_path_slice等结构,它们用于描述寄存器的webphp源码物理信息。通过配置或add_hdl_path操作,可以在寄存器模型中存储和管理多个HDL路径,对应不同的寄存器实例。

后门读写操作会调用uvm_hdl_read()函数,它是一个通过DPI-C实现的外部函数,根据编译选项的不同,可以选择使用C语言访问HDL路径。写操作成功后,会更新寄存器的镜像值并写入实际寄存器。

总结来说,实现寄存器模型后门访问的关键步骤包括设置寄存器的HDL路径,配置单个寄存器的物理信息,并确保与HDL中的实际结构对应。需要注意的是,如果寄存器在HDL中被拆分为多个字段,需正确配置这些字段的访问路径以避免警告。